Inhaltsverzeichnis

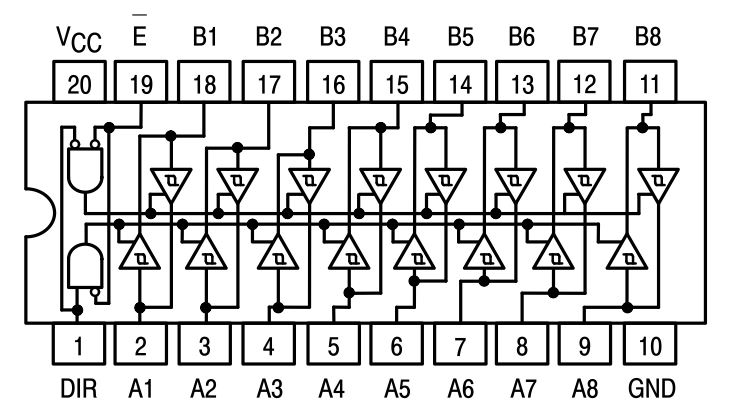

74_245 - 8 Bit Treiber

Dieser Baustein enthält acht bidirektionale Bus- Leitungstreiber mit Tristate-Ausgängen. Die Ausgänge werden niederohmig, wenn der Freigabeeingang /G=LOW ist. Anderfalls sind sie unabhängig von DIR hochohmig.

Der Eingang DIR bestimmt, in welcher Richtung der Baustein die Daten passieren läßt. Ist DIR=HIGH, dann wird EN2 aktiviert und die Daten fließen in Richtung des Pfeils von Funktionsblock 2, von A nach B. Ist DIR=LOW, so dreht sich die Datenflussrichtung um.

Alle Eingänge des Bausteins besitzen einen Schmitt-Trigger. Dieser besitzt eine Hysteresis von etwa 0,4V. Damit eignet sich der Baustein als Empfänger zur Formierung von verrauschten Signalen.

Pinbelegung / Pinout

im Amiga

| Typ | Commo-Nr. | C= Bezeichnung | C= Info | Form | Editors Info | |

|---|---|---|---|---|---|---|

| A | 318092-01 | IC 74 ALS 245 | AMIGA-2000 | DIP-20 | ||

| B | 390089-01 | IC 74 F 245 | C-128/AMIGA-2000 | DIP-20 | ||

| C | 391375-01 | IC 74 F 245 SOIC SMD | A-4091 | SO-20 | ||

| D | 391474-01 | IC 74 FCT 245 SOIC SM | A-4000 | SO-20 | ||

| E | 310003-01 | IC 74 HC 245 | AMIGA-500 | |||

| F | 380227-06 | IC 74 HCT 245 | AMIGA-2000 | DIP-20 | ?? | |

| G | 391100-01 | IC 74 HCT 245 SOIC SM | A-4000 | SO-20 | ||

| H | 390001-01 | IC 74 LS 245 | SCSI CTRL. AMIGA-2090 | |||

| I | 391142-01 | IC 74 LS 245 SMD | Amiga-600 | SO-20 | ||

| J | 901521-46 | IC 74 LS 245 | BUS BUFFER | DIP-20 |

| Vorkommen | Anzahl | Typ | Position | Bemerkung |

|---|---|---|---|---|

| A500+ | 2 | F | U40,U41, | - |

| A600 | 8 | I | U, | - |

| A | 1 | I | U, | - |

| A2000 | 2 | A | U602, U605, | - |

| A2000 | 4 | J? | U600, U601, U603, U604, | - |

| A2000 | 2 | B | U103, U105, | - |

| A | 1 | I | U, | - |

| A | 1 | I | U, | - |

| A4091 | 1 | C | U, | - |

vorübergehende Arbeitsliste

| COMMO-NO. | Rechner | Qty. | Part | Type | Form | Designator |

|---|---|---|---|---|---|---|

| x? | A1000 | ? | 74__245 | DIP-20 | U, | |

| 391142-01 | A1200-R1D4 | 4 | 74LS245 | SO- | ||

| 390089-01 | A3000-R7 | 11 | 74F245 | DIP- | U702,U708,U709,U715,U716,U257,U258,U891-94, | |

| 390089-01 | A3000-T | 11 | 74F245 | DIP- | U702,U708,U709,U715,U716,U257,U258,U891-94, | |

| 391375-01 | A4000-D | 7 | 74F245 | SO- | ||

| 391474-01 | A4000-D | 4 | 74FCT245T | SO- | ||

| 391100-01 | A4000-D | 2 | 74HCT245 | SO- | ||

| 901521-46 | CDTV | 2 | 74LS245 | DIP- | U52, U53, | |

| 310003-01 | CDTV | 2 | 74HC245 | DIP-20 | U1, U2, | |

| -- | CD32 | 0 | 74__245 | -- | keine |

Besonderheit A2000

Im A2000 sind für die Bus-Hälften zwei verschiedene Bausteine verwendet worden:

- U602 + U605 → 74ALS245

- U603 + U604 → 74LS245

|

Hintergrund ist, dass immer zwei 8-Bit breite Treiber den 16-Bit Bus bedienen. Wenn jedoch alle Bits gleichzeitig kippen, ziehen die Chips recht viel Strom, der aber von der armen 2-Lagen Platine nicht in der Geschwindigkeit geliefert werden kann. Wenn man Nur LS-Treiber einsetzt, gibt es einfach Übertragungsfehler. Setzt man für eine Bushälfte schnellere Chips ein, verteilt sich der „Stromstoß“ zeitlich, und alle Bits werden korrekt übertragen. Das mit den zwei unterschiedlichen Logikfamilien ist *eigentlich* ein no-go aka „übler Hack“. Wenn man weiß, dass dieses Problem existiert, sollte dennoch die gleiche Logikfamilie eingesetzt werden, aber die Enable-Signale zeitlich versetzt werden. |

https://www.a1k.org/forum/showpost.php?p=1211957&postcount=5

Downloads / Links

- Nachweis

- Beschreibung von www.GoBlack.de: TTL auf deutsch (leider nicht mehr online)

- Datenblätter

- SN74ALS245A Texas Instruments (1.3MB)

- 74F245SC Fairchild (109kB)

- MC74F245 Motorola (39kb)

- 74F245 National Semiconductor (180kb)

- 74FCT245 Texas Instruments (90kB)

- MM74HCT245 Fairchild (110kB)

- M74HCT245 SGS Thomson (273kB)

- DM74LS245 Fairchild (71kB)

- SN74LS245 Motorola (161kB)

- SN74LS245 old Texas Instruments (556kB)